## Introduction

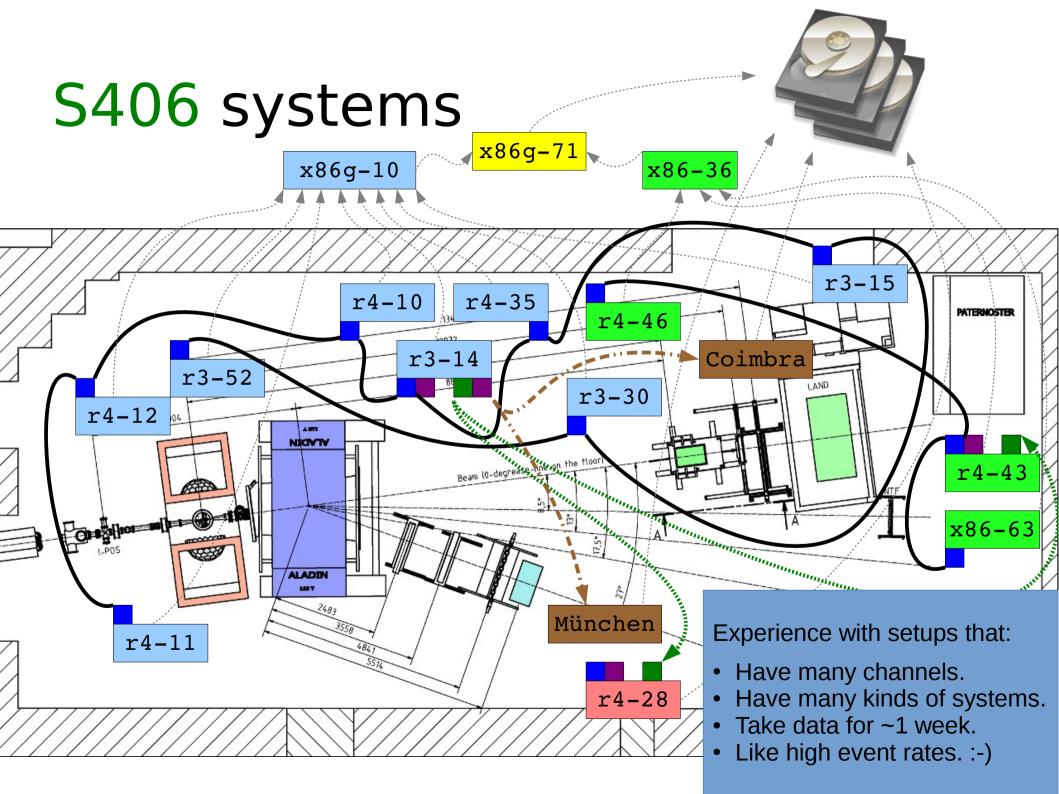

- Store slow-control information (HV settings, magnet currents...) in the data stream

- Integrate with a distributed DAQ (NuSTAR).

- Follow the DAQ topology.

- 'Normal' events not suitable:

- Just flow through the DAQ / analysis.

- Late connected clients / files would not get earlier set values.

- New concept: sticky events.

- Delivered however late the connection is.

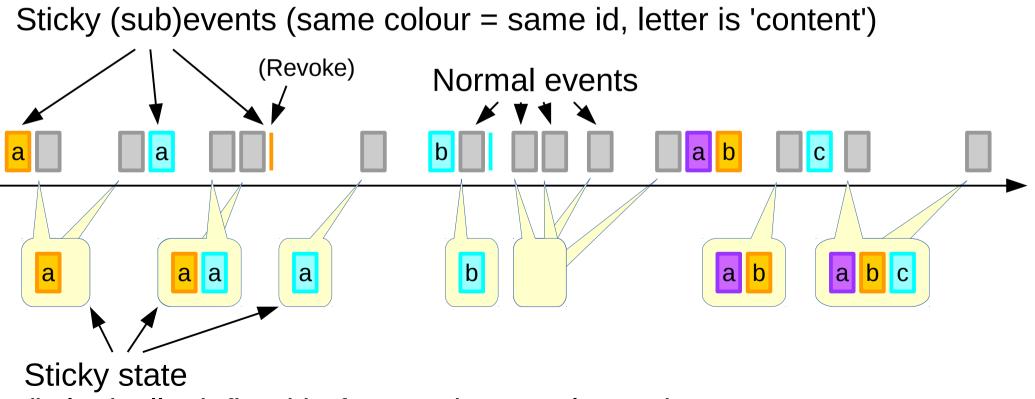

#### Sticky subevents

- Packaged in sticky events.

- The sticky thing is the subevents.

- Sticky = held active until replaced.

- Sticky subevents identified (as usual) by

- type/subtype/ctrl/crate/procid

- Removed as active with length = -1.

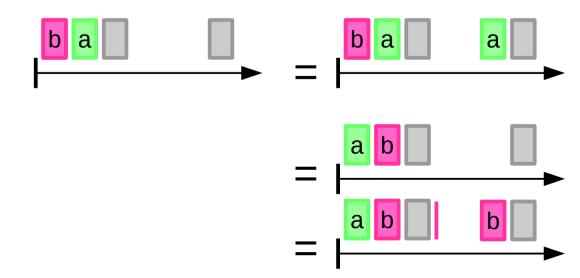

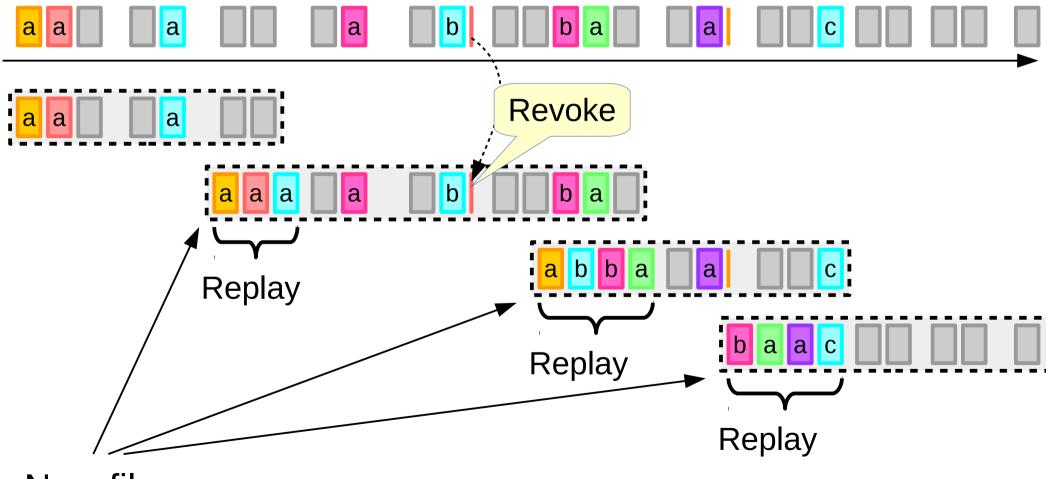

## Sticky events: simple semantics

- Sticky subevents are valid until replaced

- ... or revoked (replace by nothing)

(is logically defined before each normal event)

### **Guaranteed delivery**

An receiver (either file or network client) will before each normal event have received exactly the (at that point) active set of sticky subevents.

Sticky subevents may be delivered:

- Multiple times.

- In any order.

# DAQ / proxy servers

- Absorb the complications in standard programs.

- Keeps analysis clients simple.

Not so much a design choice, rather a lucky side-effect.

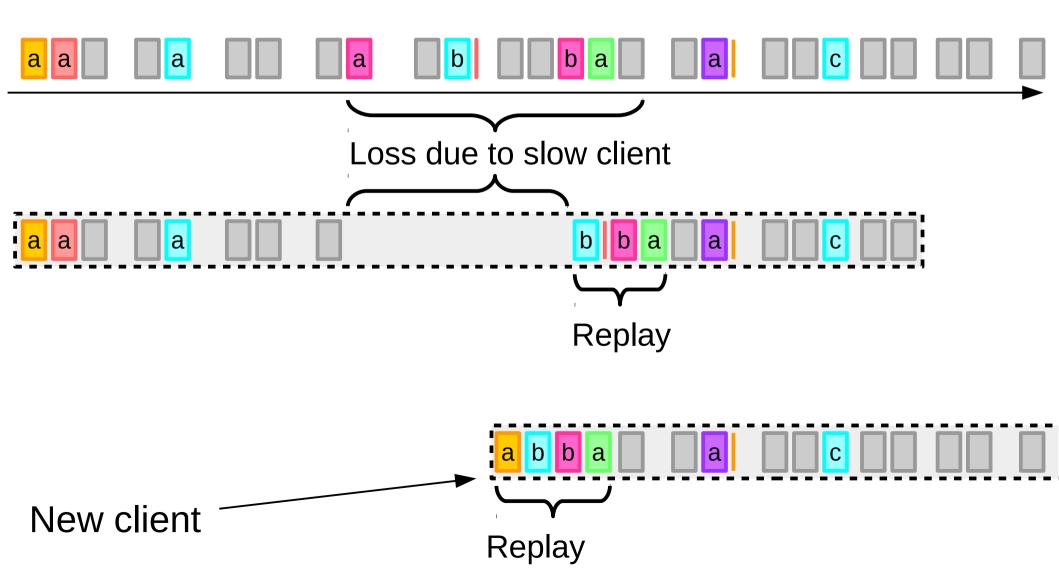

#### Output stages keep track

New files

#### Output stages keep track (network)

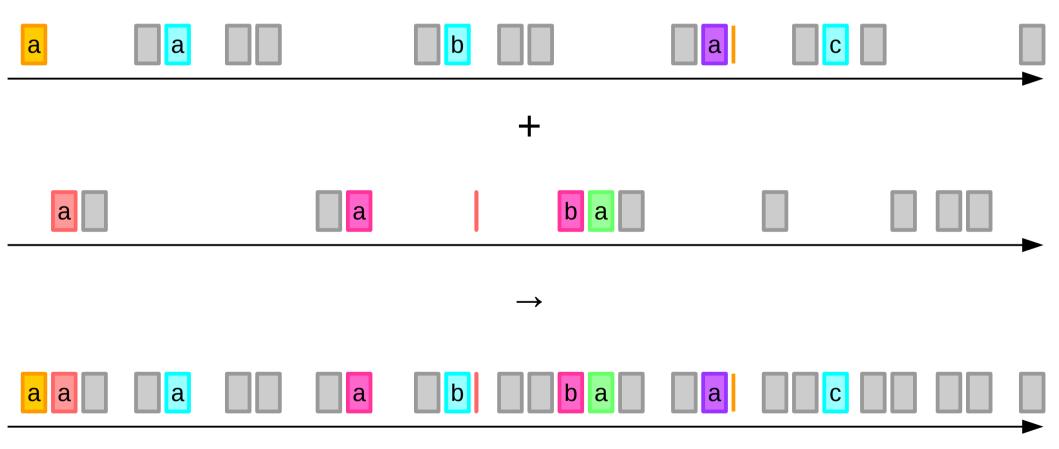

## Merging / time sorting

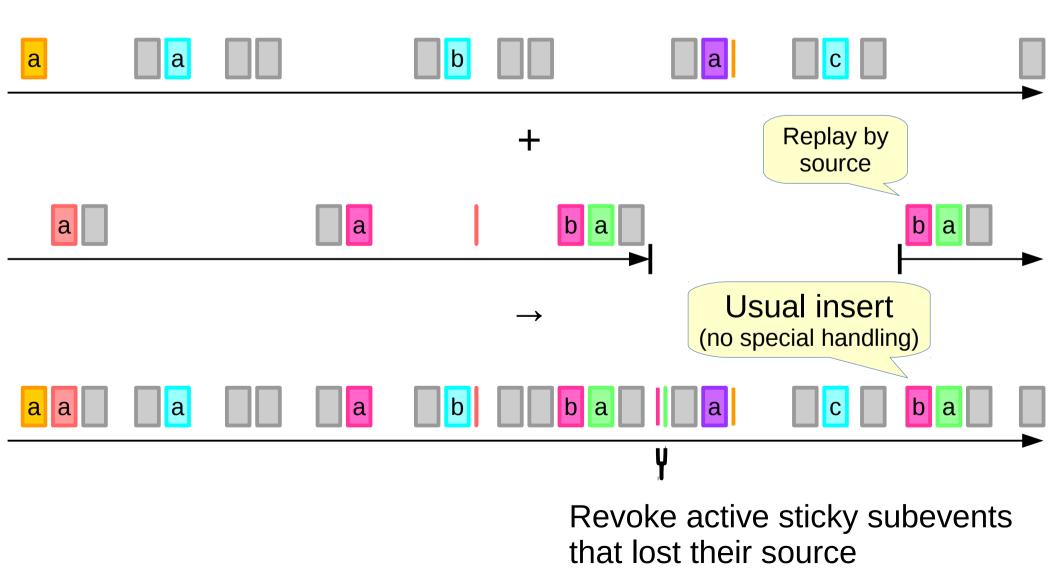

#### Merging – loss of source

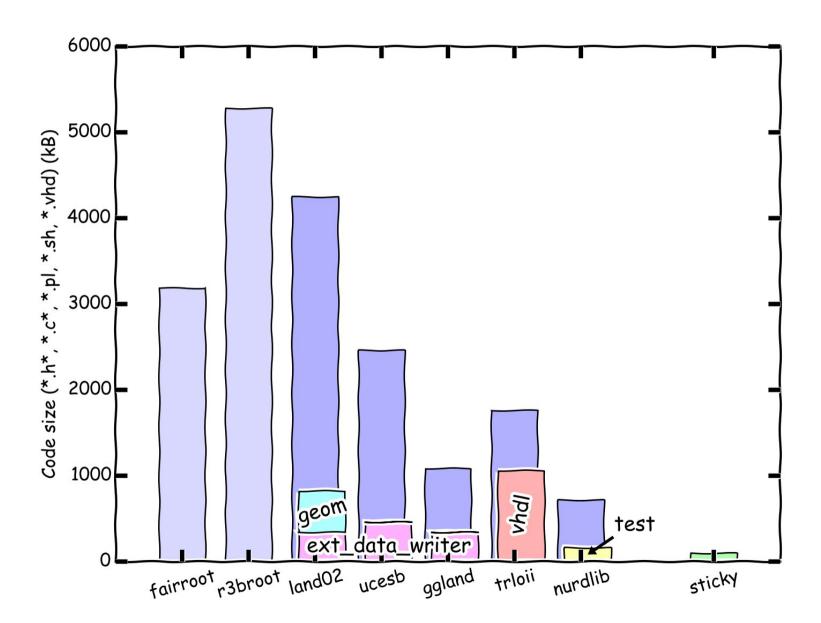

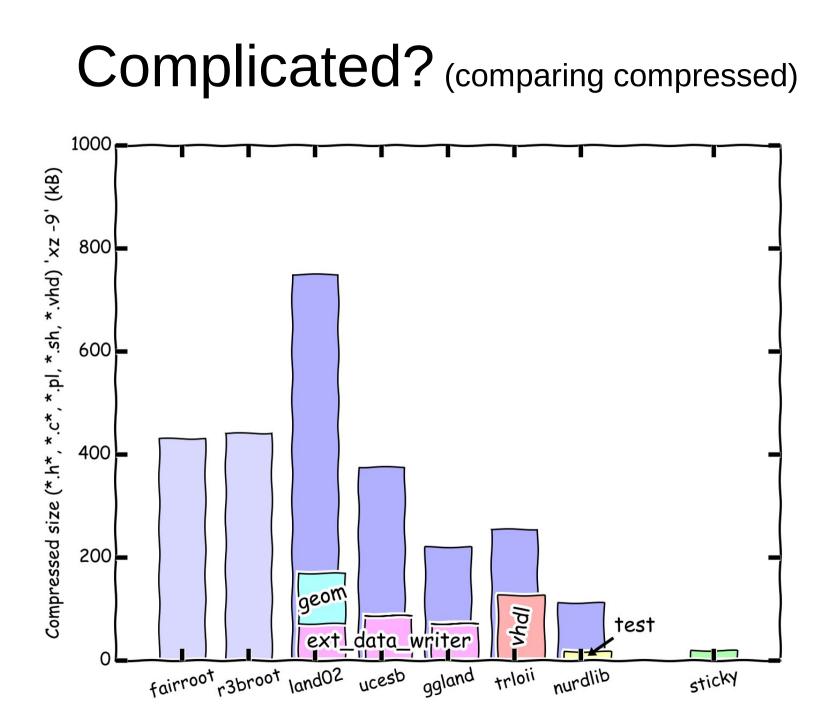

#### Complicated?

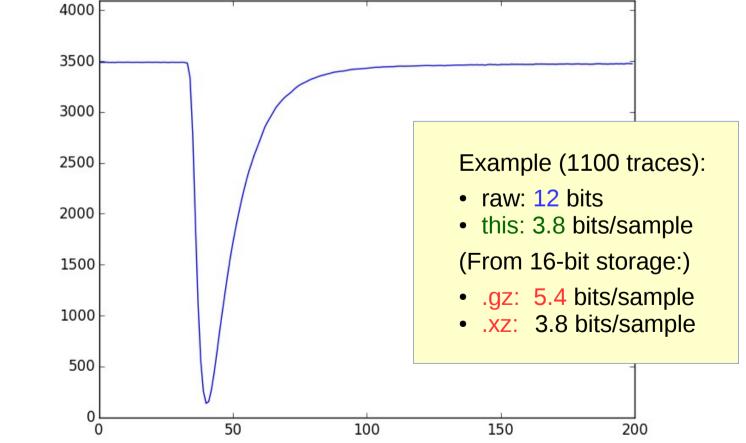

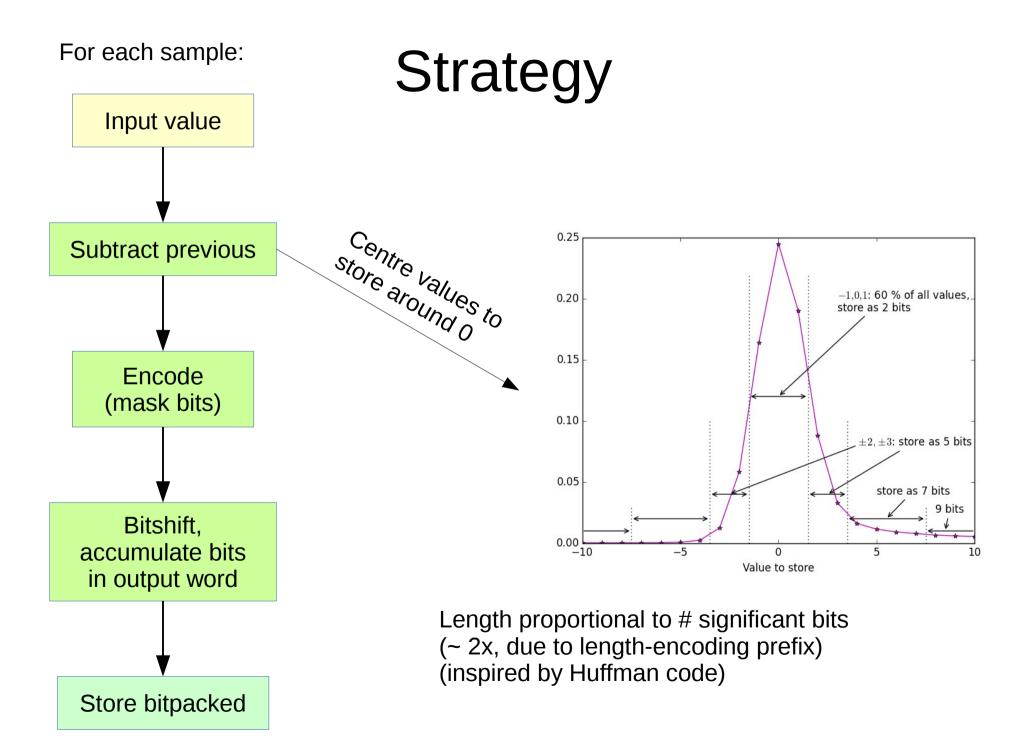

- FPGA-friendly

- Reduce:

- bandwidth

- storage

#### FPGA code

entity logcode\_compress is

generic(bits : integer);

reset

input

output

: in std logic;

: in std logic;

in\_word : in std\_logic; get last : in std logic;

out word : out std logic

: in std logic vector(bits-1 downto 0);

: out std logic vector(31 downto 0);

port (clk

);

- VHDL

- 1 sample/clock cycle (@100 MHz easily)

- Tested in testbench, data compared to C implementation.

- 550 LUTs on virtex4 (compiled, not tested)

- Dominated by large barrel shifter.

- (Could be smaller (~1/3), but with ~10-30 cycles/sample.)

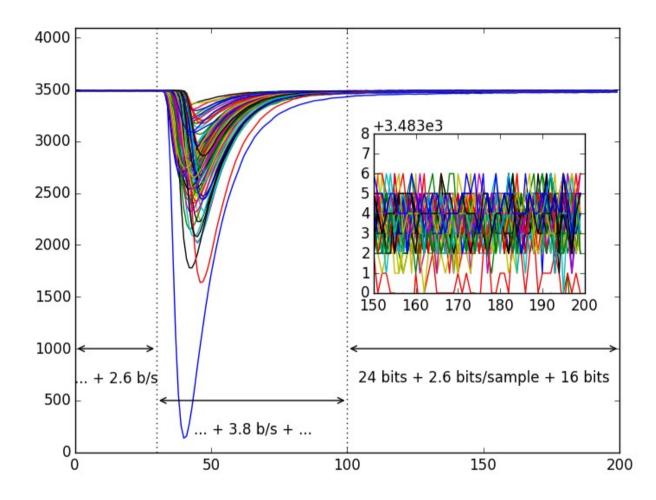

#### Some results

- Drawback: current version requires noise-level adaption

- Working on new encoding scheme: without drawback - slightly less efficient, even simpler (de)coding

# Fine! Thank you!

# Lots of

http://fy.chalmers.se/~f96hajo/shows/

Live by the compiler timing messages!