# LMD in FPGA to Time Sorter via Fakernet

Håkan T. Johansson, Subatomic Physics, Chalmers, Göteborg

> R3B Collaboration Meeting, 8-10 Nov 2023, Helmholtz Institute Mainz

### Bad news first

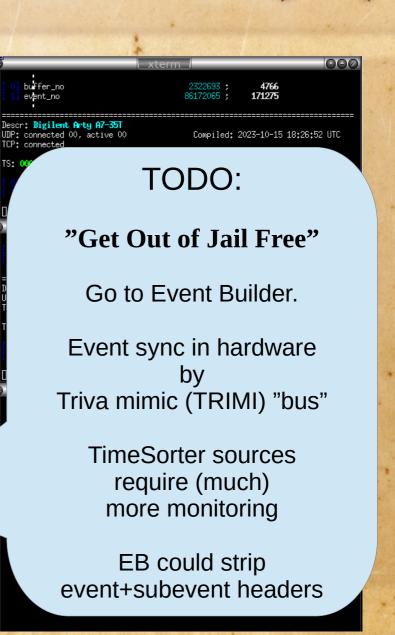

What will be presented is **not** ready for *large-scale* use.

Requires excessive monitoring...

Can be used small-scale / testing.

# Fakernet: FPGA-independent TCP + UDP

| Manufact. | Board                     | FPGA               | Ethernet |  |

|-----------|---------------------------|--------------------|----------|--|

| Digilent  | Arty A7                   | Artix 7-<br>35/100 | 100 Mbps |  |

| QMTECH    | Cyclone IV<br>Starter Kit | Cyclone IV         | 1 Gbps   |  |

| ALINX     | AX516                     | Spartan 6          | 1 Gbps   |  |

| ALINX     | AX7101                    | Artix 7-100        | 1 Gbps   |  |

| ALINX     | AX7201                    | Artix 7-100        | 1 Gbps   |  |

| • • • • • |                           | Xilinx             |          |  |

|           |                           | Altera             |          |  |

# Fakernet LMD...

Produce LMD events in FPGA

. . .

~ 1000 lines of VHDL. ~ 1000 LUTs.

```

when WAIT_EVENT =>

-- We cannot process data until there is at least one word

```

```

-- in the event buffer (the internal header).

```

```

if (has_in_word = '1') then

```

```

state <= READ_EVENT_HEADER;</pre>

```

```

elsif (i_flush = '1') then

state <= PREPARE PAD;</pre>

```

```

end if;

```

when READ\_EVENT\_HEADER =>

-- Latch the internal header data. One cycle later to allow the

-- write to the RAM block to have completed.

cur ev words <= inevh payload words;</pre>

```

cur_ev_trig <= inevh_trig;

cur ev cnt <= inevh cnt;</pre>

```

```

ts_has <= inevh_ts_has;</pre>

```

```

ts_err <= inevh_ts_err;</pre>

```

```

state <= PREPARE_EVENT;</pre>

```

when PREPARE\_EVENT =>

# Fakernet LMD => Timesorter

- Produce LMD events in FPGA

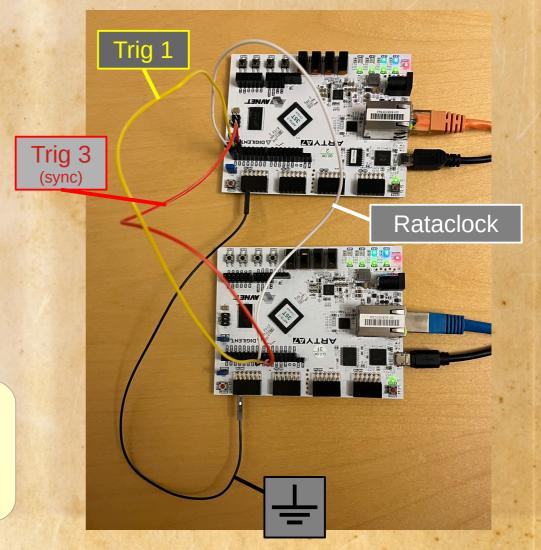

- Two boards, sync'ed with rataclock timestamps

→ Combined in drasi TS (timesorter)

- Sync triggers...

- Sync check values...

One small addition before TCP open().

# Fakernet LMD => Timesorter

- Produce LMD events in FPGA

- Two boards, sync'ed with rataclock timestamps

→ Combined in drasi TS (timesorter)

- Sync triggers: < 5 ns

- Sync check values: ok

**"Go To Jail"** Go directly to Time Sorter. Do not pass Readout, do not collect deadtime

# Fakernet LMD => Timesorter

- Produce LMD events in FPGA

- Two boards, sync'ed with rataclock timestamps

→ Combined in drasi TS (timesorter)

- Sync triggers: < 5 ns

- Sync check values: ok

**"Go To Jail"** Go directly to Time Sorter. Do not pass Readout, do not collect deadtime

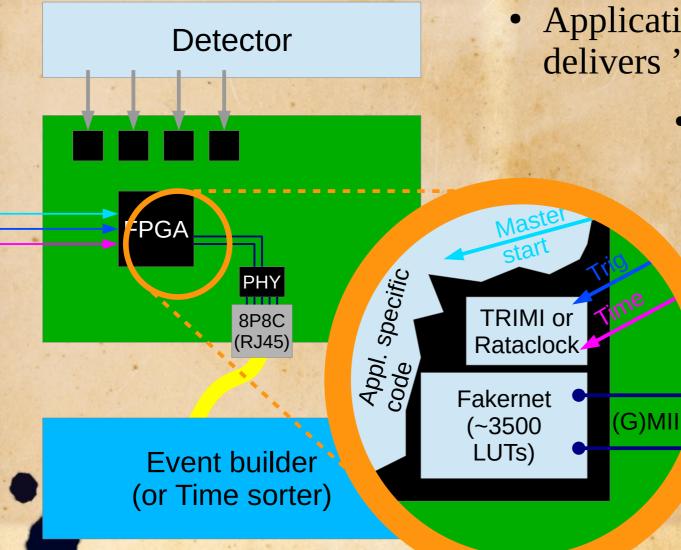

# Direct LMD from FPGA

- Application specific code delivers 'module' event data

- Format as LMD by small 'adapter' code

- Send directly to EB / TS

- Needed:

- FPGA

- PHY

- No CPU

# Fin!

### Fakernet thanks:

- Philipp Klenze The Idea!

- Anders Furufors Initial impl. help

- Gorka Landaburu External use

- Bastian Löher Rataclock popularisation

- Wonderful community tools:

- openFPGALoader

- GHDL (simulator)

- GTKWave

- Wireshark

# Fin!

### Fakernet thanks:

- Philipp Klenze The Idea!

- Anders Furufors Initial impl. help

- Gorka Landaburu External use

- Bastian Löher Rataclock popularisation

- Wonderful community tools:

- openFPGALoader

- GHDL (simulator)

- GTKWave

- Wireshark

# Thank you!

# Backup

### Fakernet in other use

#### FPGA NTP server

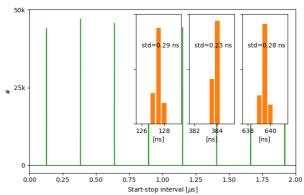

### 0.5 ns sampler

Start+stop pulses, 128+n\*256 ns apart, from board #1 to board #2.

(2) 10 -20 -20 -11.40 -20 -11.40 -20 -11.40 -20 -11.40 -20 -11.40 -20 -11.40 -11.40 -11.40 -11.40 -11.40 -11.5 ppm @ 100 MHz = 99998850 Hz (0.1 ppm = 10 Hz) -11.5 ppm @ 100 MHz = 99998850 Hz -11.60 -11.60 -11.5 ppm @ 100 MHz = 99998850 Hz -11.60 -11.60 -11.60 -11.60 -11.60 -11.5 ppm @ 100 MHz = 99998850 Hz -11.60 -11.60 -11.60 -11.60 -11.60 -11.60 -11.5 ppm @ 100 MHz = 99998850 Hz -11.60 -11.60 -11.60 -11.60 -11.60 -11.60 -11.60 -11.5 ppm @ 100 MHz = 99998850 Hz -0.60 Psm d # 2 -0.6

2500 5000

7500 10000 12500 15000 17500 2000

Time [s]