The data is generated in a user module in the FPGA, typically controlling som dedicated hardware.

The TCP data stream is compatible with the "LMD transport" protocol (as e.g. used by MBS or drasi), including the 16-byte initial header. However, due to Fakernet handling of TCP resets by a small UDP packet, this must be sent before each connection attempt.

The data is provided (committed) as events using a simple 32-bit data write interface with destination offset, such that words need not be written in order. Typical interface for generator:

port (...

-- Data input interface (for TCP stream)

event_word : out std_logic_vector(31 downto 0); -- 32-bit value to write.

event_offset : out std_logic_vector; -- Offset of value in event.

event_write : out std_logic; -- Write value this cycle.

event_commit_len: out std_logic_vector; -- Length of event to commit.

event_commit : out std_logic; -- Commit event this cycle.

event_free : in std_logic; -- Space is available for new event.

event_reset : in std_logic; -- Output buffer has been reset.

...

The event data written consists of an internal header, an optional timestamp and the payload only.

LMD event and subevent headers as well as WR timestamp marks are added by a generic formatting module.

The subevent specification (type,subtype,id,control,crate) is provided to the formatting module.

The Fakernet UDP register access interface provides control and monitoring. A simplified interface provides 32-bit setup registers and read-only status values, as well as counters (to-be-implemented (already used in fakernet internals)):

...

wr_regs : in word32_array; -- Array of 32-bit setup values.

wr_regs_strobe : in std_logic_vector; -- Strobe when value is written.

rd_regs : out word32_array; -- Read-only status values.

counters : out std_logic_vector -- Signals to be counted.

...

Load the Fakernet gateware in the usual way.

Note: run each command below in a new terminal. Easier testing overview, and some need to run in parallell.

Reconfigure the generic test gateware to use the LMD events as TCP data stream (would be default with dedicated hardware):

client/fnetctrl 192.168.1.192 --write=5:2 Wrote 0x00000005 -> 0x00000002

Read the data directly with the "LMD transport" protocol from an analysis program (e.g. UCESB):

path-to-ucesb/empty/empty --fnet=192.168.1.192 Reading mapping/calibration file 'empty/gen_empty/data_mapping.hh'... Optional map/calib file 'empty/calibration.hh' does not exist, is ok. Server '192.168.1.197' known... (IP : 192.168.1.197) (port: 1). Connecting UDP port: 15 Send TCP reset via UDP. Connecting TCP port: 1 Server data: 2 kiB chunks; prefetch buffer: 64 MiB. Processed: 50.9M (346k/s) 50.9M (346k/s) (0 errors) /

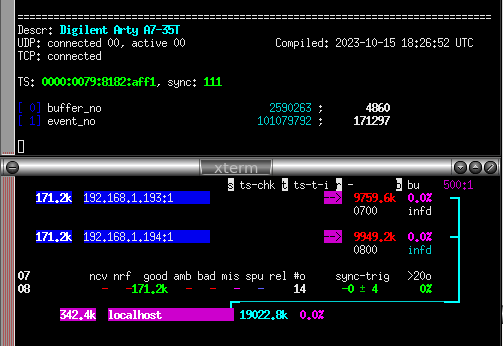

Monitor the status:

client/fnetctrl 192.168.1.192 --readout ... Descr: Digilent Arty A7-35T UDP: connected 00, active 00 Compiled: 2023-09-03 22:34:33 UTC TCP: connected [ 0] buffer_no 43231026 ; 5781 [ 1] event_no 2618871323 ; 350297 ...

Reconfigure the simulated data generation to include timestamps (here with ID 7):

client/fnetctrl 192.168.1.192 --write=0x1002:0x107 Wrote 0x00001002 -> 0x00000107

Read the data directly with a drasi time-sorter (will stop any previously running readout, e.g. by UCESB above):

path-to-drasi/bin/lwrocmerge --merge-mode=wr --log-no-start-wait --buf=size=10M --max-ev-size=32ki --fnet=192.168.1.192 --server=stream ... 10: lwroc_merge_in.c:1140: [fnet-cli: 192.168.1.197] Fakernet, protobuf=2048, max-ev-size=2048 (info message) 10: lwroc_merge_sort.c:985: [fnet-cli: 192.168.1.197] [trig: 0, eventno: 2733335560, size 64] Active sources: 1/1 (added #0)

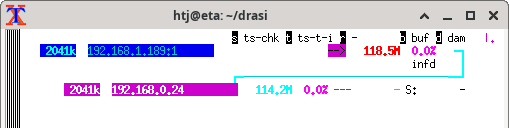

Typical drasi monitoring:

path-to-drasi/bin/lwrocmon --tree localhost

Read the drasi stream server data with UCESB and print some raw data:

path-to-ucesb/empty/empty --fnet=192.168.1.192 --print --data ... Event 129567067 Type/Subtype 10 1 Size 40 Trigger 0 SubEv ProcID 0 Type/Subtype 0 0 Size 20 Ctrl 0 Subcrate 0 00000700 03e13df9 04e13cf8 05e1029b 06e10000 Event 129567068 Type/Subtype 10 1 Size 44 Trigger 0 SubEv ProcID 0 Type/Subtype 0 0 Size 24 Ctrl 0 Subcrate 0 00000700 03e141e2 04e13cf8 05e1029b 06e10000 c000100f Event 129567069 Type/Subtype 10 1 Size 56 Trigger 0 SubEv ProcID 0 Type/Subtype 0 0 Size 36 Ctrl 0 Subcrate 0 00000700 03e145cb 04e13cf8 05e1029b 06e10000 0a0a4865 6c6c6f20 576f726c 64210a0a ...

Last modified: Mon Dec 19 09:35:58 CET 2022