Now that we understand the architecture of the Origin2000 system, it is time to address "tuning," i.e., how do we get our programs to run fast on this architecture?

We can break tuning into 5 steps:

Just as in tuning, we'll now take things one step at a time.

If you don't have to get the right answer, you can make a program run arbitrarily fast, so the very first rule in tuning is that the program has to generate the correct results. While this may seem obvious, it is quite easy to forget to check the answers along the way as one is making performance improvements. A lot of frustration can be avoided by making only one change at a time and verifying that the program is still correct after each change.

In addition to problems introduced by performance changes, correctness issues may be raised simply in porting a code from one system to another. If the program is written in a high level language and adheres to the language standard, it will generally port with no difficulties. This is particularly true for standard-compliant Fortran-77 programs, but there are some exceptions for C programs.

Irix 6.x is a 64-bit operating system. While programs may be compiled and run as if it were a 32-bit operating system, you often want to take advantage of the larger address space and compile in 64-bit mode. In this mode, both pointers and long integers are 64 bits in size, while int's remain 32 bits. If a program assumes that pointers and int's are both 32 bits long, run-time faults and/or incorrect answers can result. If this occurs, there are two remedies: either correct the program so that types of different sizes are not haphazardly intermixed, or ignore the coding problems and compile the program to run in 32-bit mode. The second solution is certainly expedient, and is even a perfectly reasonable approach for programs which will never grow beyond the confines of a 32-bit address space. But if one wishes a program to be able to exploit the advantages of the 64-bit operating system, correcting the size problems is the proper solution.

One selects which mode to compile in via the flags -32, -n32 and -64. The "mode" is more often called the ABI, or Application Binary Interface (see abi(5) for a detailed explanation of ABIs). -32 is the default ABI since it provides the highest level of portability.

However, programs compiled using this ABI not only cannot take advantage

of many of the extra capabilities of the 64-bit operating system, they also

are limited to the MIPS I and MIPS II instruction sets. If one wishes to

use the capabilities of the MIPS III or MIPS IV instructions sets, then

one needs to compile with either -n32 or -64.

With the -n32 ABI, pointers and long ints are still 32 bits in size, so one retains the

portability of the -32 ABI. -n32 differs from -32 in that instead of generating programs with just the MIPS I or MIPS II ISAs, it allows programs to be generated using either the MIPS III or MIPS

IV ISAs, as selected by the -mips3 and -mips4 flags, respectively. With the -64 flag, pointers and long ints are 64 bits in length, so full advantage may

be taken of the 64-bit operating system. As with -n32, either the MIPS III or MIPS IV ISAs may be chosen.

On Origin2000 (and all other non-R8000) systems, the default ABI and ISA

are -32 -mips2; on R8000-based systems, the defaults are -64 -mips4. Because the defaults vary by system type, it is highly recommended that

the desired ABI and ISA be explicitly declared for each compilation. The

clearest way to do this is to specify these options directly in a makefile

(see make(1) and pmake(1)) so they are used by all compilation commands:

ABI = -n32

ISA = -mips4

CFLAGS = $(ABI) $(ISA) -Ofast

.

.

.

.c.o:

$(CC) $(CFLAGS) -c $<

An alternative approach is to to make use of a defaults specification file. This is a file which tells the compiler which ABI and ISA it should use if none have been specified in the compilation command. The system adminstrator may create the file /etc/compiler.defaults to set the defaults for a particular system. Individual users may create their own compiler.defaults files and then tell the compiler where to look for them by setting the environment variable COMPILER_DEFAULTS_PATH; the first such file found in this colon-separated path list will take precedence over the system-wide file. If a default specification file has been provided, its contents will override the compiler's built-in defaults (but not the options specified explicitly in the compilation command).

The contents of the compiler.defaults file must be the the following specifier:

-DEFAULT:[abi={32|n32|64}]:[isa={mips1|mips2|mips3|mips4}]:[proc={r4k|r5k|r8k|r10k}]

which allows one to indicate the default ABI and ISA, as well as which processor to compile for (more on this option later).

One final method is available for specifying the ABI. One can set the environment variable SGI_ABI to -32, -n32 or -64 to specify the default ABI. If this environment variable is set, it will override the setting in the defaults specification file; a command line setting, however, will take precedence over this environment variable.

Unless it is a requirement that the binary can be run on an R4000-based system (which supports MIPS III, but not MIPS IV), use one of the following ABI/ISA combinations

% cc -64 -mips4 ...

% cc -n32 -mips4 ...

for C, and similarly for the other languages. The same ABI (but not necessarily ISA) must be used for all objects comprising a single executable. Different executables may use different ABIs, however. For more information on these compiler flags, as well as the defaults specification file, see the man pages for cc(1), f77(1), CC(1), f90(1), ld(1).

A program can fail to port for other reasons. Since different compilers handle standards violations differently, non-standard-compliant programs often generate different results when rehosted. An often seen example of this is a Fortran program which assumes that all variables are initialized to 0. While this initialization occurred on most older machines, it is not done in general on newer, stack-based architectures. When a program making such an assumption is rehosted to a new machine, it will almost certainly generate incorrect results.

To detect this error, one can compile with the -trapuv flag. This flag initializes all unitialized variables in a program with the value 0xFFFA5A5A. When this value is used as a floating point variable, it is treated as a floating point NaN and it will cause a floating point trap. When it is used as a pointer, an address or segmentation violation will most likely occur. By running the program with a debugger, such as dbx(1), the use of such an uninitialized variable can be pinpointed, and the program can then be fixed to do the proper initialization.

While fixing the program is the "right thing to do," it does require some

effort by the programmer. An alternative, which requires almost no effort,

is to use the -static flag. This flag causes all variables to be allocated from a static data

area rather than the stack, and these variables will then be initialized

to 0. There is a cost to the easy way out, however. Use of the -static flag generally hurts program performance; a 20% penalty is not uncommon.

Another trick which can sometimes help in rehosting a program is to compile

with the lowest optimization level, -O0 (i.e., no optimization), but this, too will significantly hurt performance.

Other types of porting failures can occur as well. The results generated on one computer may disagree with those from another computer because of differences in the floating point format, or compiler differences which cause the roundoff error to change. One needs to understand the particular program in order to determine if these differences are significant. In addition, some programs may fail to even compile on a new system if extensions are not supported or are provided with a different syntax; Fortran pointers provide a good example of this. In such situations, the code must be modified to be compatible with the new compiler. Similarly, if a program makes calls to a particular vendor's libraries, these calls will need to be replaced with equivalent entry points from the new vendor's libraries.

Finally, programs sometimes have mistakes in them which by pure luck had previously not caused problems. But when compiled on a new system, errors finally appear. Writing beyond the end of an array can show this behavior. Such mistakes need to be corrected. For f77 compilations, one can use the -C (or, equivalently, -check_bounds) flag to instruct the Fortran compiler to generate code for runtime subscript range checking. If an out-of-bounds array reference is made, the program will abort and display an error message indicating the illegal reference which was made and which line of code it occurred on:

Subscript out of range on file line 6, procedure MAIN_. Attempt to access the 0-th element of variable ?. *** Execution Terminated (99) ***

When tracking down the source of incorrect results, a symbolic debugger is an invaluable tool. Two such debuggers are available for the Origin2000 system. dbx is the standard Unix debugger which has been available for many years. It uses a simple, teletype style interface and may be used to debug sequential programs or multi-processor programs, although the MP debugging is somewhat awkward. cvd, the WorkShop debugger, uses a graphical user interface and provides greater fuctionality and efficiency than dbx; it is also much more convenient for debugging multi-processor programs. For information on how to use these products, consult the dbx(1) reference page and the Developer Magic: Debugger User's Guide.

The quickest and easiest way to improve the performance of a program is to link it with libraries already tuned for the target hardware. In addition to the standard libraries, such as libc, whose hardware-specific versions are automatically linked in with programs compiled and run on the Origin2000 system, there are two other libraries which may optionally be used which can provide substantial performance benefits.

libfastm provides highly optimized versions of a subset of the routines found in libm, the standard math library. Optimized scalar versions of sin, cos, tan, exp, log, and pow for both single- and double-precision are provided. To link in libfastm, append -lfastm to the end of the link line:

cc -o program <objects> -lfastm Separate versions of libfastm exist for the R10000, R8000 and R5000. In order to link with the correct

version, the desired chip should be explicitly requested with the -r10000, -r8000 or -r5000 flags, respectively. When used on the compile line, these flags also instruct

the compiler to generate code scheduled for the specified chip. For Origin2000

systems, the -r10000 flag should be used when compiling and linking.

In addition the scalar routines just mentioned, the following vector intrinsics are now part of the standard math library: vacos, vasin, vatan, vcos, vexp, vlog, vsin, vsqrt and vtan, plus the single precision versions whose names are derived from those of these double precision versions by appending an f. This library is linked in automatically by Fortran; the -lm flag should be used when linking with ld or the C compiler:

cc -o program <objects> -lmMore information on the math intrinsics can be found in math(3M) and libfastm(3M), and an description of when the compiler will use the vector math intrinsics automatically is presented later.

complib.sgimath The other library which provides optimized code is complib.sgimath. This is a library of mathematical routines for carrying out linear algebra operations, FFTs and convolutions. It contains optimized implementations of the public domain libraries LINPACK, EISPACK, LAPACK, FFTPACK, and the Level-1, -2 and -3 BLAS, plus proprietary sparse solvers tuned specifically for Silicon Graphics, Inc. platforms.

Many of the complib routines have been parallelized, so there are separate sequential and parallel

versions of the library. To link in the sequential version of complib.sgimath, add -lcomplib.sgimath to the link line:

f77 -o program <objects> -lcomplib.sgimath -lfastm To link in the parallel version, use -lcomplib.sgimath_mp; in addition, the -mp flag must be used when linking in the parallel code:

f77 -mp -o program <objects> -lcomplib.sgimath_mp -lfastm Since complib.sgimath uses some routines found in libfastm, libfastm should be linked in after complib.sgimath.

For more information about these libraries, see the man pages for libfastm(3M), math(3M), complib(3F), blas(3F), lapack(3F), fft(3F), conv(3F), solvers(3F), psldu(3F), psldlt(3F), and pskysl(3F).

When confronted with a program composed of hundreds of modules and thousands of lines of code, it would require a very heroic, and very inefficient, effort to tune the entire program. Tuning needs to be concentrated on those few sections of the code where the work will pay off with the biggest gains in performance. These sections of code are identified with the help of a profiler.

The hardware counters in the R10000 CPU make it possible to profile the behavior of a program in many ways without modifying the code. The software tools are:

You use these tools to find out what constrains the program, and which parts of the it consume the most time. Through the use of a combination of these tools, it is possible to identify most performance problems.

The profiling tools depend for most of their features on the R10000's Performance Counter Registers. These on-chip registers can be programmed to count hardware events as they happen, for example machine cycles, instructions, branch predictions, floating point instructions, or cache misses.

There are only two Performance Counter registers. Each can be programmed to count machine cycles or one of 15 other events, for a total of 32 events that can be counted (30 of which are distinct). The specific events are summarized in the following table which can always be obtained by using the command perfex -h. A detailed discussion of the events is contained in this sidebar on counter definitions.

| Event Number | Counter 0 Event | Event Number | Counter 1 Event |

|---|---|---|---|

| 0 | Cycles | 16 | Cycles |

| 1 | Instructions issued to functional units | 17 | Instructions graduated |

| 2 | Memory data access (load, prefetch, sync, cacheop) issued | 18 | Memory data loads graduated |

| 3 | Memory stores issued | 19 | Memory data stores graduated |

| 4 | Store-conditionals issued | 20 | Store-conditionals graduated |

| 5 | Store-conditionals failed | 21 | Floating-point instructions graduated |

| 6 | Branches decoded | 22 | Quadwords written back from L1 cache |

| 7 | Quadwords written back from L2 cache | 23 | TLB refill exceptions |

| 8 | Correctable ECC errors on L2 cache | 24 | Branches mispredicted |

| 9 | L1 cache misses (instruction) | 25 | L1 cache misses (data) |

| 10 | L2 cache misses (instruction) | 26 | L2 cache misses (data) |

| 11 | L2 cache way mispredicted (instruction) | 27 | L2 cache way mispredicted (data) |

| 12 | External intervention requests | 28 | External intervention request hits in L2 cache |

| 13 | External invalidate requests | 29 | External invalidate request hits in L2 cache |

| 14 | Instructions done (formerly, virtual coherency condition) | 30 | Stores, or prefetches with store hint, to CleanExclusive L2 cache blocks |

| 15 | Instructions graduated | 31 | Stores, or prefetches with store hint, to Shared L2 cache blocks. |

The counters are 64-bit integers. When a counter overflows, a hardware trap occurs. The kernel can preload a counter with (2^64 - n) to cause a trap after n counts occur. The profiling tools use this capability. For example, the command ssrun -gi_hwc programs the graduated instruction counter (event 17) to overflow every 32K counts. Each time the counter overflows, ssrun samples the program counter and stack state of the subject program.

The reference page r10k_counters(5) gives detailed information on how the counters can be accessed through the /proc interface. This is the interface used by the profiling tools. The interface hides the division of events between only two registers, and allows the software to view the counters as a single set of 32, 64-bit counters. The operating system time-multiplexes the active counters between the events being counted. This requres sampling and scaling, and can introduce some error when more than two events are counted.

In general, it is better to access the counters through the profiling tools. A program that uses the counter interface directly cannot be profiled using perfex, nor using ssrun for any experiment that depends on counters. When a program must access counter values directly, the simplest interface is through libperfex, documented in the libperfex(3) reference page.

The simplest profiling tool is perfex, documented in the perfex(1) reference page. It runs a subject program and records data about the run, similar to timex(1):

% perfex [options] command [arguments]

The subject program and its arguments are given. perfex sets up the counter interface and forks the subject program. When the program ends, perfex writes counter data to standard output.

perfex gathers its information with no modifications to your existing program. While this is very convenient, the data obtained come from the entire run of the program. If you only want to profile a particular section of the program, you will need to use the library interface to perfex, libperfex(3). To use this interface, you insert into your program's source code a call to initiate counting and another to terminate it; a third call is used to print the counts gathered. The program must then be linked with the libperfex library:

% f77|cc -o program <objects> -lperfex

Since you can use SpeedShop to see where in a program various event counts come from, we will not describe libperfex in detail. More information can be found in its reference page.

Using perfex options you specify what is to be counted. You can specify one or two countable events. In this case, the counts are absolute and accurate. For example, the command

% perfex -e 15 -e 21 adi2

runs the subject program and reports the exact counts of graduated instructions and graduated floating point instructions. You use this mode when you want to explore specific points of program behavior.

When you specify option -a (all events), perfex multiplexes all 32 events over the program run. Each count is active 1/16 of the time, and then scaled by 16. The resulting counts have some statistical error. The error is small (and the counts are sufficiently repeatable) provided that the subject program runs in a stable execution mode for a number of seconds. When the program runs for a short time, or shifts between radically different regimes of instruction or data use, the counts are less dependable and less repeatable. Nevertheless, perfex -a usually gives a good overview of program operation.

Here is the perfex command line and output applied to a sample program called adi2:

% perfex -a -x adi2 WARNING: Multiplexing events to project totals--inaccuracy possible. Time: 7.990 seconds Checksum: 5.6160428338E+06 0 Cycles...................................................... 1645481936 1 Issued instructions......................................... 677976352 2 Issued loads................................................ 111412576 3 Issued stores............................................... 45085648 4 Issued store conditionals................................... 0 5 Failed store conditionals................................... 0 6 Decoded branches............................................ 52196528 7 Quadwords written back from scache.......................... 61794304 8 Correctable scache data array ECC errors.................... 0 9 Primary instruction cache misses............................ 8560 10 Secondary instruction cache misses.......................... 304 11 Instruction misprediction from scache way prediction table.. 272 12 External interventions...................................... 6144 13 External invalidations...................................... 10032 14 Virtual coherency conditions................................ 0 15 Graduated instructions...................................... 371427616 16 Cycles...................................................... 1645481936 17 Graduated instructions...................................... 400535904 18 Graduated loads............................................. 90474112 19 Graduated stores............................................ 34776112 20 Graduated store conditionals................................ 0 21 Graduated floating point instructions....................... 28292480 22 Quadwords written back from primary data cache.............. 32386400 23 TLB misses.................................................. 5687456 24 Mispredicted branches....................................... 410064 25 Primary data cache misses................................... 16330160 26 Secondary data cache misses................................. 7708944 27 Data misprediction from scache way prediction table......... 663648 28 External intervention hits in scache........................ 6144 29 External invalidation hits in scache........................ 6864 30 Store/prefetch exclusive to clean block in scache........... 7582256 31 Store/prefetch exclusive to shared block in scache.......... 8144

The -x option requests that perfex also gather counts for kernel code that handles exceptions, so the work

done by the OS to handle TLB misses is included in these counts.

The raw event counts are interesting but it is more useful to convert them to elapsed time. Some time estimates are simple, for example dividing the cycle count by the machine clock rate gives elapsed run time (1645481936/195MHZ = 8.44 seconds). Other events are not so simple, and can only be stated in terms of a range of times. For example, the time to handle a primary cache miss varies depending on whether the needed data are in the secondary cache, or in memory, or in the cache of another CPU. Analysis of this kind can be requested using perfex -a -x -y.

When you use -a , -x and -y, perfex collects and displays all event counts, but it also displays a report of estimated times based on the counts. Here is an example, again of the program adi2:

% perfex -a -x -y adi2

WARNING: Multiplexing events to project totals--inaccuracy possible.

Time: 7.996 seconds

Checksum: 5.6160428338E+06

Based on 196 MHz IP27

Typical Minimum Maximum

Event Counter Name Counter Value Time (sec) Time (sec) Time (sec)

===================================================================================================================

0 Cycles...................................................... 1639802080 8.366337 8.366337 8.366337

16 Cycles...................................................... 1639802080 8.366337 8.366337 8.366337

26 Secondary data cache misses................................. 7736432 2.920580 1.909429 3.248837

23 TLB misses.................................................. 5693808 1.978017 1.978017 1.978017

7 Quadwords written back from scache.......................... 61712384 1.973562 1.305834 1.973562

25 Primary data cache misses................................... 16368384 0.752445 0.235504 0.752445

22 Quadwords written back from primary data cache.............. 32385280 0.636139 0.518825 0.735278

2 Issued loads................................................ 109918560 0.560809 0.560809 0.560809

18 Graduated loads............................................. 88890736 0.453524 0.453524 0.453524

6 Decoded branches............................................ 52497360 0.267844 0.267844 0.267844

3 Issued stores............................................... 43923616 0.224100 0.224100 0.224100

19 Graduated stores............................................ 33430240 0.170562 0.170562 0.170562

21 Graduated floating point instructions....................... 28371152 0.144751 0.072375 7.527040

30 Store/prefetch exclusive to clean block in scache........... 7545984 0.038500 0.038500 0.038500

24 Mispredicted branches....................................... 417440 0.003024 0.001363 0.011118

9 Primary instruction cache misses............................ 8272 0.000761 0.000238 0.000761

10 Secondary instruction cache misses.......................... 768 0.000290 0.000190 0.000323

31 Store/prefetch exclusive to shared block in scache.......... 15168 0.000077 0.000077 0.000077

1 Issued instructions......................................... 673476960 0.000000 0.000000 3.436107

4 Issued store conditionals................................... 0 0.000000 0.000000 0.000000

5 Failed store conditionals................................... 0 0.000000 0.000000 0.000000

8 Correctable scache data array ECC errors.................... 0 0.000000 0.000000 0.000000

11 Instruction misprediction from scache way prediction table.. 432 0.000000 0.000000 0.000002

12 External interventions...................................... 6288 0.000000 0.000000 0.000000

13 External invalidations...................................... 9360 0.000000 0.000000 0.000000

14 Virtual coherency conditions................................ 0 0.000000 0.000000 0.000000

15 Graduated instructions...................................... 364303776 0.000000 0.000000 1.858693

17 Graduated instructions...................................... 392675440 0.000000 0.000000 2.003446

20 Graduated store conditionals................................ 0 0.000000 0.000000 0.000000

27 Data misprediction from scache way prediction table......... 679120 0.000000 0.000000 0.003465

28 External intervention hits in scache........................ 6288 0.000000 0.000000 0.000000

29 External invalidation hits in scache........................ 5952 0.000000 0.000000 0.000000

Statistics

=========================================================================================

Graduated instructions/cycle................................................ 0.222163

Graduated floating point instructions/cycle................................. 0.017302

Graduated loads & stores/cycle.............................................. 0.074595

Graduated loads & stores/floating point instruction......................... 5.422486

Mispredicted branches/Decoded branches...................................... 0.007952

Graduated loads/Issued loads................................................ 0.808696

Graduated stores/Issued stores.............................................. 0.761099

Data mispredict/Data scache hits............................................ 0.078675

Instruction mispredict/Instruction scache hits.............................. 0.057569

L1 Cache Line Reuse......................................................... 6.473003

L2 Cache Line Reuse......................................................... 1.115754

L1 Data Cache Hit Rate...................................................... 0.866185

L2 Data Cache Hit Rate...................................................... 0.527355

Time accessing memory/Total time............................................ 0.750045

L1--L2 bandwidth used (MB/s, average per process)........................... 124.541093

Memory bandwidth used (MB/s, average per process)........................... 236.383187

MFLOPS (average per process)................................................ 3.391108

"Maximum," "minimum," and "typical" time cost estimates are reported. Each is obtained by consulting an internal table which holds the "maximum," "minimum," and "typical" costs for each event, and multiplying this cost by the count for the event. Event costs are usually measured in terms of machine cycles, and so the cost of an event generally depends on the clock speed of the processor, which is also reported in the output.

The "maximum" value contained in the table corresponds to the worst case cost of a single occurrence of the event. Sometimes this can be a very pessimistic estimate. For example, the maximum cost for graduated floating point instructions assumes that all such instructions are double precision reciprocal square roots, since that is the most costly R10000 floating point instruction.

Due to the latency-hiding capabilities of the R10000, the "minimum" cost of virtually any event could be zero since most events can be overlapped with other operations. To avoid simply reporting minimum costs of 0, which would be of no practical use, the "minimum" time reported by perfex -y corresponds to the best case cost of a single occurrence of the event. The "best case" cost is obtained by running the maximum number of simultaneous occurrences of that event and averaging the cost. For example, two floating point instructions can complete per cycle, so the best case cost is 0.5 cycles per floating point instruction.

The "typical" cost falls somewhere between "minimum" and maximum" and is meant to correspond to the cost one would expect to see in average programs.

perfex -y prints the event counts and associated cost estimates sorted from most costly to least costly. While resembling a profiling output, this is not a true profile. The event costs reported are only estimates. Furthermore, since events do overlap with each other, the sum of the estimated times will usually exceed the program's run time. This output should only be used to identify which events are responsible for significant portions of the program's run time, and to get a rough idea of what those costs might be.

For the example above, it is clear that the program is spending a significant fraction of its time in handling secondary cache and TLB misses. To make a significant improvement in the runtine of this program, the tuning measures need to be concentrated on reducing those cache misses.

In addition the event counts and cost estimates, perfex -y also reports a number of statistics derived from the typical costs. The

meaning of many of the statistics is self-evident, for example, Graduated instructions/cycle. Below we list those statistics whose definitions require more explanation:

Data mispredict/Data scache hits

Instruction mispredict/Instruction scache hits

L1 Cache Line Reuse

L2 Cache Line Reuse

L1 Data Cache Hit Rate

L2 Data Cache Hit Rate

Time accessing memory/Total time

L1--L2 bandwidth used (MB/s, average per process)

Memory bandwidth used (MB/s, average per process)

MFLOPS (MB/s, average per process)

These statistics can give you a quick way to identify performance problems

in your program. For example, the cache hit rate statistics tell you how

cache-friendly your program is. Since a secondary cache miss is much more

expensive than a cache hit, the L2 Data Cache Hit Rate needs to be quite close to 1 for the program to not be paying a large penalty

for the cache misses. Values above about 0.96 indicate good cache performance.

Note that for the above example, the rate is 0.53, further confirmation

of the cache problems in this program.

There is nothing magical about the output of perfex, and you are free to write your analysis tools. For example, this awk script processes the output of perfex -a and reorders it, inserting derived ratios after the absolute count lines. You can write other simple scripts that extract the counter values of particular interest in a given situation.

The purpose of profiling is to find out exactly where a program is spending its time; that is, in precisely which procedures or lines of code. Then you can concentrate your efforts on the (usually small) areas of code where there is the most to be gained.

You do profiling using the SpeedShop package. It supports these methods of profiling:

SpeedShop can sample based on a variety of time bases: the system timer,

or any of several of the R10000 Performance Counters.

The SpeedShop package has three parts:

These programs are documented in the following reference pages, which you should print and save for frequent reference:

The accuracy of sampling depends on the time base that sets the sampling interval. In each case, the time base is the independent variable, and the program state is the dependent variable. You select from the sampling methods summarized in this table:

| ssrun Option | Time Base | Comments |

|---|---|---|

| -usertime | 30ms timer | Fairly coarse resolution; experiment runs quickly and output file is small; some bugs noted in speedshop(1). |

| -pcsamp[x] -fpcsamp[x] | 10ms timer 1ms timer | Moderately coarse resolution; functions that cause cache misses or page faults are emphasized. Suffix x for 32-bit counts. |

| -gi_hwc -fgi_hwc | 32771 insts 6553 insts | Fine-grain resolution based on graduated instructions. Emphasizes functions that burn a lot of instructions. |

| -cy_hwc -fcy_hwc | 16411 clocks 3779 clocks | Fine-grain resolution based on elapsed cycles. Emphasizes functions with cache misses and mispredicted branches. |

| -ic_hwc -fic_hwc | 2053 icache miss 419 icache miss | Emphasizes code that doesn't fit in L1 cache. |

| -isc_hwc -fisc_hwc | 131 scache miss 29 scache miss | Emphasizes code that doesn't fit in L2 cache. Should be coarse-grained measure. |

| -dc_hwc -fdc_hwc | 2053 dcache miss 419 dcache miss | Emphasizes code that causes L1 cache data misses. |

| -dsc_hwc -fdsc_hwc | 131 scache miss 29 scache miss | Emphasizes code that causes L2 cache data misses. |

| -tlb_hwc -ftlb_hwc | 257 TLB miss 53 TLB miss | Emphasizes code that causes page faults. |

| -gfp_hwc -fgfp_hwc | 32771 fp insts 6553 fp insts | Emphasizes code that performs heavy FP calculation. |

| -prof_hwc | user-set | Hardware counter and overflow value from environment variables. |

Each time base finds the program PC more often in the code that consumes the most units of that time base:

It is easy to perform an experiment. Here is the application of an experiment to program adi2:

% ssrun -fpcsamp adi2 Time: 7.619 seconds Checksum: 5.6160428338E+06

The output file of samples is left in a file with the default name of ./command.experiment.pid. In this case the name was adi2.fpcsamp.4885. However, it is often more convenient to dictate the name of the output file. You can do this by putting the desired filename and directory in environment variables. Using this csh script you can run an experiment, passing the output directory and filename on the command line, for example

% ssruno -d /var/tmp -o adi2.cy -cy_hwc adi2 ssrun -cy_hwc adi2 .................................. Time: 9.644 seconds Checksum: 5.6160428338E+06 .................................. ssrun ends. -rw-r--r-- 1 guest guest 18480 Dec 17 16:25 /var/tmp/adi2.cy

Regardless of which time base you use for sampling, you display the result using prof. By default, prof displays a list of procedures ordered from the one with the most samples to the least:

% prof adi2.fpcsamp.4885

-------------------------------------------------------------------------------

Profile listing generated Sat Jan 4 10:28:11 1997

with: prof adi2.fpcsamp.4885

-------------------------------------------------------------------------------

samples time CPU FPU Clock N-cpu S-interval Countsize

8574 8.6s R10000 R10010 196.0MHz 1 1.0ms 2(bytes)

Each sample covers 4 bytes for every 1.0ms ( 0.01% of 8.5740s)

-------------------------------------------------------------------------------

-p[rocedures] using pc-sampling.

Sorted in descending order by the number of samples in each procedure.

Unexecuted procedures are excluded.

-------------------------------------------------------------------------------

samples time(%) cum time(%) procedure (dso:file)

6688 6.7s( 78.0) 6.7s( 78.0) zsweep (adi2:adi2.f)

671 0.67s( 7.8) 7.4s( 85.8) xsweep (adi2:adi2.f)

662 0.66s( 7.7) 8s( 93.6) ysweep (adi2:adi2.f)

208 0.21s( 2.4) 8.2s( 96.0) fake_adi (adi2:adi2.f)

178 0.18s( 2.1) 8.4s( 98.1) irand_ (/usr/lib32/libftn.so:../../libF77/rand_.c)

166 0.17s( 1.9) 8.6s(100.0) rand_ (/usr/lib32/libftn.so:../../libF77/rand_.c)

1 0.001s( 0.0) 8.6s(100.0) __oserror (/usr/lib32/libc.so.1:oserror.c)

8574 8.6s(100.0) 8.6s(100.0) TOTAL

From this profile, it is clear that our attention needs to be focused on

the routine zsweep, since it consumes almost 80% of the runtime of this program.

For finer detail, use the -heavy option. This supplements the list of procedures with a list of individual source line numbers, ordered by frequency:

-------------------------------------------------------------------------------

-h[eavy] using pc-sampling.

Sorted in descending order by the number of samples in each line.

Lines with no samples are excluded.

-------------------------------------------------------------------------------

samples time(%) cum time(%) procedure (file:line)

3405 3.4s( 39.7) 3.4s( 39.7) zsweep (adi2.f:122)

3226 3.2s( 37.6) 6.6s( 77.3) zsweep (adi2.f:126)

425 0.42s( 5.0) 7.1s( 82.3) xsweep (adi2.f:80)

387 0.39s( 4.5) 7.4s( 86.8) ysweep (adi2.f:101)

273 0.27s( 3.2) 7.7s( 90.0) ysweep (adi2.f:105)

246 0.25s( 2.9) 8s( 92.9) xsweep (adi2.f:84)

167 0.17s( 1.9) 8.1s( 94.8) irand_ (../../libF77/rand_.c:62)

163 0.16s( 1.9) 8.3s( 96.7) fake_adi (adi2.f:18)

160 0.16s( 1.9) 8.5s( 98.6) rand_ (../../libF77/rand_.c:69)

45 0.045s( 0.5) 8.5s( 99.1) fake_adi (adi2.f:59)

32 0.032s( 0.4) 8.5s( 99.5) zsweep (adi2.f:113)

21 0.021s( 0.2) 8.5s( 99.7) zsweep (adi2.f:121)

11 0.011s( 0.1) 8.6s( 99.8) irand_ (../../libF77/rand_.c:63)

6 0.006s( 0.1) 8.6s( 99.9) rand_ (../../libF77/rand_.c:67)

4 0.004s( 0.0) 8.6s(100.0) zsweep (adi2.f:125)

1 0.001s( 0.0) 8.6s(100.0) ysweep (adi2.f:104)

1 0.001s( 0.0) 8.6s(100.0) ysweep (adi2.f:100)

1 0.001s( 0.0) 8.6s(100.0) __oserror (oserror.c:127)

8574 8.6s(100.0) 8.6s(100.0) TOTAL

From this listing it is clear that lines 122 and 126 warrant further inspection. Even finer detail can be obtained with the -source option, which lists the source code and disassembled machine code, indicating sample hits on specific instructions.

The other type of profiling is called ideal time, or basic block, profiling. Basic block is a compiler term for a section of code which has only one entrance and one exit. Any program can be decomposed into basic blocks.

To obtain an ideal profile, ssrun makes a copy of the executable program and modifies the copy to contain code that records the entry to each basic block. Not only the executable itself, but also all DSOs that it links to are copied and instrumented. The instrumented executable and libraries are statically linked and run:

% ssrun -ideal adi2

Beginning libraries

/usr/lib32/libssrt.so

/usr/lib32/libss.so

/usr/lib32/libfastm.so

/usr/lib32/libftn.so

/usr/lib32/libm.so

/usr/lib32/libc.so.1

Ending libraries, beginning "adi2"

Time: 8.291 seconds

Checksum: 5.6160428338E+06

The number of times each basic block was encountered is recorded. The output data file is displayed using prof, just as for a sampled run. The report ranks source and library procedures from most-used to least:

% prof adi2.ideal.4920

Prof run at: Sat Jan 4 10:34:06 1997

Command line: prof adi2.ideal.4920

285898739: Total number of cycles

1.45867s: Total execution time

285898739: Total number of instructions executed

1.000: Ratio of cycles / instruction

196: Clock rate in MHz

R10000: Target processor modelled

---------------------------------------------------------

Procedures sorted in descending order of cycles executed.

Unexecuted procedures are not listed. Procedures

beginning with *DF* are dummy functions and represent

init, fini and stub sections.

---------------------------------------------------------

cycles(%) cum % secs instrns calls procedure(dso:file)

68026368(23.79) 23.79 0.35 68026368 32768 xsweep(adi2.pixie:adi2.f)

68026368(23.79) 47.59 0.35 68026368 32768 ysweep(adi2.pixie:adi2.f)

68026368(23.79) 71.38 0.35 68026368 32768 zsweep(adi2.pixie:adi2.f)

35651584(12.47) 83.85 0.18 35651584 2097152 rand_(./libftn.so.pixn32:../../libF77/rand_.c)

27262976( 9.54) 93.39 0.14 27262976 2097152 irand_(./libftn.so.pixn32:../../libF77/rand_.c)

18874113( 6.60) 99.99 0.10 18874113 1 fake_adi(adi2.pixie:adi2.f)

11508( 0.00) 99.99 0.00 11508 5 memset(./libc.so.1.pixn32:/slayer_xlv0/ficussg-nov05/work/irix/lib/libc/libc_n32_M4/strings/bzero.s)

3101( 0.00) 99.99 0.00 3101 55 __flsbuf(./libc.so.1.pixn32:_flsbuf.c)

2446( 0.00) 100.00 0.00 2446 42 x_putc(./libftn.so.pixn32:../../libI77/wsfe.c)

1234( 0.00) 100.00 0.00 1234 2 x_wEND(./libftn.so.pixn32:../../libI77/wsfe.c)

1047( 0.00) 100.00 0.00 1047 1 f_exit(./libftn.so.pixn32:../../libI77/close.c)

1005( 0.00) 100.00 0.00 1005 5 fflush(./libc.so.1.pixn32:flush.c)

639( 0.00) 100.00 0.00 639 4 do_fio64_mp(./libftn.so.pixn32:../../libI77/fmt.c)

566( 0.00) 100.00 0.00 566 3 wrt_AP(./libftn.so.pixn32:../../libI77/wrtfmt.c)

495( 0.00) 100.00 0.00 495 6 map_luno(./libftn.so.pixn32:../../libI77/util.c)

458( 0.00) 100.00 0.00 458 14 op_gen(./libftn.so.pixn32:../../libI77/fmt.c)

440( 0.00) 100.00 0.00 440 9 gt_num(./libftn.so.pixn32:../../libI77/fmt.c)

414( 0.00) 100.00 0.00 414 1 getenv(./libc.so.1.pixn32:getenv.c)

.

.

.

The -heavy option adds a list of source lines, sorted by their consumption of ideal instruction cycles.

An ideal profile shows exactly and repeatedly which statements are most

executed, and gives you a very exact view of the algorithmic complexity

of the program. An ideal profile does not necessarily reflect where a program

spends its time, since it cannot take cache and TLB misses into account.

Consequently, the results of the ideal profile are startlingly different

than that of the PC sampling profile. These ideal results indicate that zsweep should take exactly the same amount of runtime as ysweep and xsweep. These differences can be used to infer where cache performance issues

exist. On machines without the R10000's hardware profiling registers, such

comparisons are the only profiling method available to locate cache problems.

Since ideal profiling counts the instructions executed by the program, it can provide all sorts of interesting information about the program. Already printed in the standard prof output are counts of how many times each subroutine is called. In addition, you may use the -op option to prof to get a listing detailing the counts of all instructions in the program. In particular, this will provide an exact count of the floating point operations executed:

% prof -op adi2.ideal.4920

Prof run at: Wed Jan 15 14:42:54 1997

Command line: prof -op adi2.ideal.4920

285898739: Total number of cycles

1.45867s: Total execution time

285898739: Total number of instructions executed

1.000: Ratio of cycles / instruction

196: Clock rate in MHz

R10000: Target processor modelled

---------------------------------------------------------

pixstats summary

---------------------------------------------------------

56590456: Floating point operations (38.796 Mflops @ 196 MHz)

105500230: Integer operations (72.3265 M intops @ 196 MHz)

.

.

.

Note that this is different than what one obtains using perfex. The R10000 counter #21 counts floating point instructions, not floating point operations. As a result, in a program which executes

a lot of multiply-add instructions --- each of which carries out 2 floating

point operations --- perfex's MFLOPS statistic can be off by a factor of almost 2. Since prof -op records all instructions executed, it counts each multiply-add instruction

as two floating point operations, thus providing the correct tally. The Mlops figure it calculates, however, is based on the ideal time, so to calculate

floating point performance, you should divide the number of floating point

operations counted by prof -op by wall clock time.

Either method of profiling, PC sampling or ideal, can be applied to multi-processor runs just as easily as it is applied to single-processor runs: each thread of an application maintains its own histogram, and the histograms may be printed individually or merged in any combination and printed as one profile.

One of the limitations of the prof output for either PC sampling or ideal time is that the information reported

contains no information about the call hierarchy. That is, if the routine zsweep in the above example were called from two different locations in the program,

we would have no idea how much time results from the call at each location;

we would only know the total time spent in zsweep. If we knew that, say, the first location was responsible for the majority

of the time, this could affect how we tune the program. For example, we

might try inlining the call into the first location, but not bother with

the second. Or, if we wanted to parallelize the program, knowing that the

first location is where the majority of the time is spent, we might consider

parallelizing the calls to zsweep there rather than trying to parallelize the zsweep routine itself.

SpeedShop provides two methods of obtaining hierarchical profiling information.

The first method is called gprof and it is used in conjunction with the ideal time profile. To obtain the gprof information for the above example, we simply add the flag -gprof to the prof command:

% prof -gprof adi2.ideal.4920

Prof run at: Wed Jan 15 16:52:09 1997

Command line: prof -gprof adi2.ideal.4920

285898739: Total number of cycles

1.45867s: Total execution time

285898739: Total number of instructions executed

1.000: Ratio of cycles / instruction

196: Clock rate in MHz

R10000: Target processor modelled

---------------------------------------------------------

Procedures sorted in descending order of cycles executed.

Unexecuted procedures are not listed. Procedures

beginning with *DF* are dummy functions and represent

init, fini and stub sections.

---------------------------------------------------------

cycles(%) cum % secs instrns calls procedure(dso:file)

68026368(23.79) 23.79 0.35 68026368 32768 xsweep(adi2.pixie:adi2.f)

68026368(23.79) 47.59 0.35 68026368 32768 ysweep(adi2.pixie:adi2.f)

68026368(23.79) 71.38 0.35 68026368 32768 zsweep(adi2.pixie:adi2.f)

35651584(12.47) 83.85 0.18 35651584 2097152 rand_(./libftn.so.pixn32:../../libF77/rand_.c)

27262976( 9.54) 93.39 0.14 27262976 2097152 irand_(./libftn.so.pixn32:../../libF77/rand_.c)

.

.

.

All times are in milliseconds.

--------------------------------------------------------------------------------

NOTE: any functions which are not part of the call

graph are listed at the end of the gprof listing

--------------------------------------------------------------------------------

self kids called/total parents

index cycles(%) self(%) kids(%) called+self name index

self kids called/total children

[1] 285895481(100.00%) 57( 0.00%) 285895424(100.00%) 0 __start [1]

50 285895369 1/1 main [2]

3 0 1/1 __istart [112]

2 0 1/1 __readenv_sigfpe [113]

--------------------------------------------------------------------------------

50 285895369 1/1 __start [1]

[2] 285895419(100.00%) 50( 0.00%) 285895369(100.00%) 1 main [2]

18874113 267020445 1/1 fake_adi [3]

205 606 5/5 signal [44]

--------------------------------------------------------------------------------

18874113 267020445 1/1 main [2]

[3] 285894558(100.00%) 18874113( 6.60%) 267020445(93.40%) 1 fake_adi [3]

68026368 0 32768/32768 zsweep [4]

68026368 0 32768/32768 ysweep [5]

68026368 0 32768/32768 xsweep [6]

35651584 27262976 2097152/2097152 rand_ [7]

28 13486 2/2 s_wsfe64 [9]

26 5368 2/2 e_wsfe [17]

22 2610 1/1 do_fioxr4v [25]

22 2610 1/1 do_fioxr8v [24]

23 2428 1/1 s_stop [28]

114 44 2/2 dtime_ [68]

--------------------------------------------------------------------------------

68026368 0 32768/32768 fake_adi [3]

[4] 68026368(23.79%) 68026368(100.00%) 0( 0.00%) 32768 zsweep [4]

--------------------------------------------------------------------------------

68026368 0 32768/32768 fake_adi [3]

[5] 68026368(23.79%) 68026368(100.00%) 0( 0.00%) 32768 ysweep [5]

--------------------------------------------------------------------------------

68026368 0 32768/32768 fake_adi [3]

[6] 68026368(23.79%) 68026368(100.00%) 0( 0.00%) 32768 xsweep [6]

--------------------------------------------------------------------------------

.

.

.

This produces the usual ideal time profiling output, but following that

is the hierarchical information. There is a block of information for each

subroutine in the program. A number, shown in brackets (e.g., [1]), is assigned to each routine so that the information pertaining to it

can easily be located in the output. Let's look in detail at the block of

information provided; we'll use fake_adi [3] as an example.

The line beginning with the number [3] shows, from left to right:

fake_adi [3].

Above this line are lines showing which routines fake_adi [3] was called from. In this case, it is only called from one place, main [2], so there is just one line (in general, there would be one line for each

routine which calls fake_adi [3]). This line shows:

fake_adi [3] due to the call from main [2];

fake_adi [3]'s descendsants due to the call from main [2];

fake_adi [3] in main [2] / the total number of calls to fake_adi [3] from all places in the program.

Since fake_adi [3] is only called once, all the time in it and its descendants is due to this

one call.

Below the line beginning with the number [3] are all the decendants of fake_adi [3]. For each of the descendants we see:

fake_adi [3]'s grandchildren);

fake_adi [3] / the total number of calls to the descendant from all places in the program.

This block of information allows us to determine not just which subroutines, but which paths in the program, are responsible for the majority of time. The only limitation to this is that gprof reports ideal time, so cache misses are not represented.

Since gprof only reports ideal time, it would be nice to have a way to get hierarchical profiling information which accurately accounts for all time in the program, the way PC sampling does. Well, there is a way, and it is called usertime profiling. For this type of profiling, the program is sampled during the run. At each sample, not only is the location of the program counter noted, but the entire call stack is traced to record which routines have been called in order to get to this point in the program. From this a hierarchical profile is constructed. Since unwinding the call stack is a reasonably expensive operation, the sampling period is for usertime profiling is relatively long: 30 milliseconds.

usertime profiling is performed with the following command:

% ssrun -usertime adi2

The output is written to a file called ./adi2.usertime.pid, where pid is the process ID for this run of adi2. The profile is displayed using prof just as for PC sampling and ideal time profiling:

% prof adi2.usertime.19572

The output is as follows:

-------------------------------------------------------------------------------

Profile listing generated Wed Jan 15 16:57:10 1997

with: prof adi2.usertime.19572

-------------------------------------------------------------------------------

Total Time (secs) : 9.99

Total Samples : 333

Stack backtrace failed: 0

Sample interval (ms) : 30

CPU : R10000

FPU : R10010

Clock : 196.0MHz

Number of CPUs : 1

-------------------------------------------------------------------------------

index %Samples self descendents total name

[1] 100.0% 0.00 9.99 333 __start

[2] 100.0% 0.00 9.99 333 main

[3] 100.0% 0.09 9.90 333 fake_adi

[4] 80.8% 8.07 0.00 269 zsweep

[5] 7.5% 0.75 0.00 25 xsweep

[6] 6.9% 0.69 0.00 23 ysweep

[7] 3.9% 0.12 0.27 13 rand_

[8] 2.7% 0.27 0.00 9 irand_

The information is less detailed than that provided by gprof, but when combined with what we know from gprof, we can get a complete hierarchical profile for all routines which have run long enough to be sampled.

As described above, PC sampling can be performed using a variety of time bases for the sampling interval. We have already seen examples of [f]pcsamp, which uses a constant time base of either 1 or 10 milliseconds, and usertime, which uses a constant time base of 30 milliseconds. The other time bases which may be used are the R10000 counter registers.

These counters can be programmed to generate an interrupt after counting

an event a specified number of times; this is called the overflow value. This interrupt is then used to generate a profile. The most commonly

used counters have been given names so that they may be used directly with

the ssrun command. These are:

[f]gi_hwc: graduate instructions

[f]cy_hwc: cycle counter

[f]ic_hwc: primary instruction cache misses

[f]isc_hwc: secondary instruction cache misses

[f]dc_hwc: primary data cache misses

[f]dsc_hwc: secondary datacache misses

[f]tlb_hwc: TLB misses

[f]gfp_hwc: graduated floating point instructions

The f-variants sample at a faster rate by setting the overflow to a lower value. The overflow values for these experiment types were givenin the table above.

In addition to these named counters, a catch-all experiment type, prof_hwc, has been provided so that counters which have not been explicitly named may also be sampled. The counter number and overflow value are specified via environment variables as follows:

% setenv _SPEEDSHOP_HWC_COUNTER_NUMBER <cntr> % setenv _SPEEDSHOP_HWC_COUNTER_OVERFLOW <ovfl>

As an example, let's sample TLB misses in adi2:

% ssrun -tlb_hwc adi2

Time: 7.887 seconds

Checksum: 5.6160428338E+06

% prof adi2.tlb_hwc.18520

-------------------------------------------------------------------------------

Profile listing generated Wed Jan 15 19:27:52 1997

with: prof adi2.tlb_hwc.18520

-------------------------------------------------------------------------------

Counter : TLB misses

Counter overflow value: 257

Total numer of ovfls : 21181

CPU : R10000

FPU : R10010

Clock : 195.0MHz

Number of CPUs : 1

-------------------------------------------------------------------------------

-p[rocedures] using counter overflow.

Sorted in descending order by the number of overflows in each procedure.

Unexecuted procedures are excluded.

-------------------------------------------------------------------------------

overflows(%) cum overflows(%) procedure (dso:file)

21169( 99.9) 21169( 99.9) zsweep (adi2:adi2.f)

4( 0.0) 21173(100.0) ysweep (adi2:adi2.f)

4( 0.0) 21177(100.0) xsweep (adi2:adi2.f)

4( 0.0) 21181(100.0) fake_adi (adi2:adi2.f)

21181(100.0) TOTAL

The profile reports the number of overflows of the TLB miss counter which occurred in each subroutine. To get the total number of TLB misses, which is what perfex would report, we need to multiply by the overflow value, 257.

This profile confirms that virtually all the TLB misses occur in the routine zsweep.

Floating point exceptions that are not specifically handled by the program (using the handle_sigfpes library procedure, documented in the handle_sigfpes(3C) reference pages) cause hardware traps nevertheless, and then are ignored in software. A high number of ignored exceptions can cause a program to run slowly for no apparent reason.

The ssrun experiment -fpe creates a trace file that records all floating point exceptions. You use prof to display the profile as usual. The report shows the procedures and lines that caused exceptions. In effect, this is a sampling profile in which the sampling time base is the occurrence of an exception.

You can use exception profiling to verify that a program does not have significant exceptions. When you know that, you may safely set a higher level of exception handling for the compiler using -TENV:X which can sometimes provide a small gain in performance.

When a program does generate a significant number of exceptions, this is almost invariably due to floating point underflows (a large number of divide-by-zero or invalid operations are likely to be fatal to the progam!). A large number of underflows will cause performance problems since, unless they are flushed to zero in hardware, they will be handled by software in the operating system kernel. So a lot of underflows will generate a lot of traps to the kernel to finish the calculations. While the results will be correct, excess system time will result. On R8000-based systems, the default is to flush underflows to zero, but on R10000-, R5000- and R4400-based systems, the default is to let the kernel handle the gradual underflow.

If gradual underflow is not required for numerical accuracy, underflows can be flushed to zero. This can be done by two methods, both of which are described in detail in handle_sigfpes(3C):

libfpe, and use the TRAP_FPE environment variable or the handle_sigfpes subroutine call to indicate that underflows be flushed to 0. The environment

variable is very easy to use:

% ld -o program ... -lfpe % setenv TRAP_FPE "UNDERFL=ZERO" % program ...

Important Note: If you have compiled the program with a higher than default value for

the -TENV:X flag, you should not use libfpe to enable any exceptions which the compiler now assumes are not enabled.

This could very easily result in the program generating mysterious floating

point exceptions. For example, if you compile with -TENV:X=3, the compiler assumes that floating point divide-by-zero exceptions are

turned off. As a result, it may replace an innocent construct such as

if (x .ne. 0.0) b = 1.0/x

with the following speculative code

tmp = 1.0/x

if (x .ne. 0.0) b = tmp

which may divide by zero. If the divide-by-zero exception is disabled, this

speculative code cannot cause problems since if tmp is ever infinity, it is not stored in b. However, if libfpe has been used to enable the divide-by-zero exception, your program will

abort if the calculation of tmp divides by zero, and it could be pretty painful to figure out what happened.

set_fpc_csr() call from within the program to explicitly set the hardware bit controlling

whether underflows are flushed to 0. This is done as follows cf. the handle_sigfpes(3C) man page:

#include <sys/fpu.h>

void

flush_to_zero(int on_off)

{

union fpc_csr n;

n.fc_word = get_fpc_csr();

if ( on_off == 0 ) {

n.fc_struct.flush = 0;

} else {

n.fc_struct.flush = 1;

}

set_fpc_csr(n.fc_word);

}

The hardware bit which controls how underflows are handled is located in a part of the R10000 floating point unit called the floating point status register (FSR). In addition to setting the way underflows are treated, this register is also used to select which IEEE rounding mode is used and which IEEE exceptions are enabled (i.e., not ignored). Furthermore, it contains the floating point condition bits, which are set by floating point compare instructions, and cause bits, which are set when any floating point exception occurs (whether or not the exception is ignored). This register is documented in the MIPS R10000 Microprocessor User's Manual.

The fpc_csr union, defined in <sys/fpu.h>, mirrors the floating point status register. One can set/clear bits in

the FSR using this union. All one needs do is retrieve the current value

of the FSR using get_fpc_csr(), set/clear the appropriate bit(s) in the fpc_csr union, and then call set_fpc_csr() to write the updated values into the register.

The names of the bits are given in the union definition:

/*

* Structure and constant definisions for the floating-point control

* control and status register (fpc_csr).

*/

#ifdef _LANGUAGE_C

union fpc_csr {

unsigned int fc_word;

struct {

#ifdef _MIPSEB

unsigned fcc : 7; /* only used for mips4 */

unsigned flush : 1;

unsigned condition : 1;

unsigned reserved1 : 5;

unsigned ex_unimplemented : 1;

unsigned ex_invalid : 1;

unsigned ex_divide0 : 1;

unsigned ex_overflow : 1;

unsigned ex_underflow : 1;

unsigned ex_inexact : 1;

unsigned en_invalid : 1;

unsigned en_divide0 : 1;

unsigned en_overflow : 1;

unsigned en_underflow : 1;

unsigned en_inexact : 1;

unsigned se_invalid : 1;

unsigned se_divide0 : 1;

unsigned se_overflow : 1;

unsigned se_underflow : 1;

unsigned se_inexact : 1;

unsigned rounding_mode : 2;

} fc_struct;

};

#endif /* _LANGUAGE_C */

The only bits which control actions are the flush bit (flush), the enable bits (en_*) and the rounding mode bits (rounding_mode).

Setting the flush bit to 1 means underflows are flushed to zero in hardware. Setting it to 0 means that underflows are not flushed to zero: they will generate an unimplemented instruction exception which tells the OS to perform gradual underflow in software.

The enable bits turn on various IEEE exceptions if set to 1; they disable them if set to 0. The names pretty much explain what they do (except that underflows are potentially pre-empted by the flush bit).

Finally, the 4 IEEE rounding modes are:

Any floating point option can be controlled by writing a routine like the one above which sets/ clears the appropriate FSR bits.

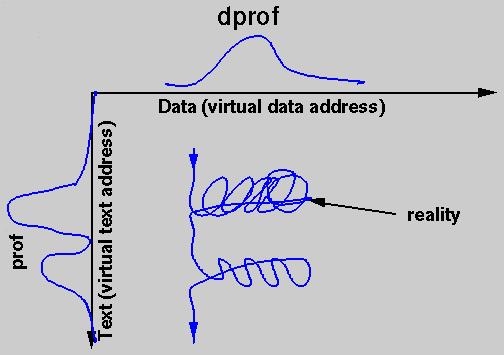

Speedshop and perfex profile the execution path, but there is a second dimension to program behavior: data references.

The dprof tool, like ssrun, executes a program and samples the program while it runs. Unlike ssrun, dprof does not sample the PC and stack. It samples the current operand address of the interrupted instruction, and accumulates a histogram of access to data addresses, grouped in virtual page units. The following is an example of running dprof on adi2:

% dprof -hwpc -out adi2.dprof adi2 Time: 27.289 seconds Checksum: 5.6160428338E+06 % ls -l adi2.dprof -rw-r--r-- 1 guest 40118 Dec 18 18:54 adi2.dprof % cat adi2.dprof -------------------------------------------------- address thread reads writes -------------------------------------------------- 0xfffeff4000 0 168 11 0xfffeff8000 0 228 7 0xfffeffc000 0 156 11 0xffff000000 0 126 7 0xffff004000 0 153 9 0xffff008000 0 71 12 0xffff00c000 0 40 3 0xffff010000 0 116 10 0xffff014000 0 219 38 0xffff018000 0 225 73 0xffff01c000 0 193 53 0xffff020000 0 127 41 0xffff024000 0 246 31 0xffff028000 0 147 18 0xffff02c000 0 50 23 0xffff030000 0 87 47 0xffff034000 0 134 36 0xffff038000 0 165 37 0xffff03c000 0 136 37 0xffff040000 0 98 32 ... 0xfffffe8000 0 389 46 0xfffffec000 0 481 50 0xffffff0000 0 262 36 0xffffff4000 0 35 8

Each line contains a count of all references from one program thread (one IRIX process, but this program has only a single process) to one virtual memory page. (The addresses at the left increment by 0x04000, or 16KB.)

dprof operates by statistical sampling; it does not record all references. The time base is either the interval timer (option -itimer) or the R10000 event cycle counter (option -hwpc). The default interrupt frequency using the cycle counter samples only about 1 instruction in 10000. This produces a coarse sample that is not likely to be repeatable from run to run. However, even this sampling rate slows program execution by almost 3 times.

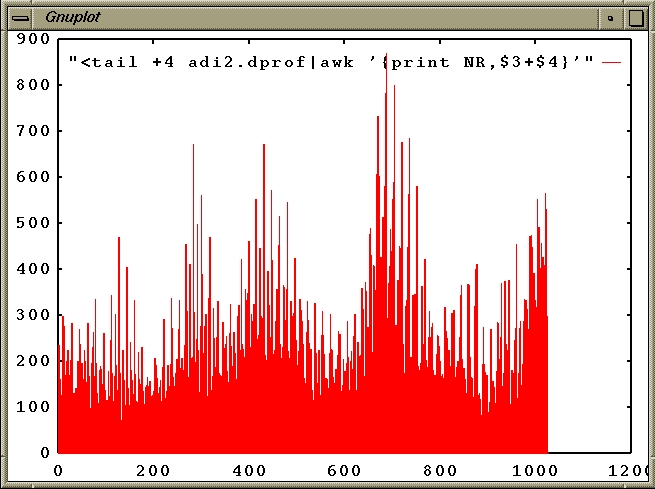

You can obtain a more detailed sample by specifying a shorter overflow count (option -ovfl), but this will extend program execution time proportionately. The coarse histogram is useful for showing which pages are used. For example, you can plot the data as a histogram. Using gnuplot (which is available on the SGI Freeware CDROM), a simple plot of total access density is obtained as follows:

% /usr/freeware/bin/gnuplot

G N U P L O T

unix version 3.5

patchlevel 3.50.1.17, 27 Aug 93

last modified Fri Aug 27 05:21:33 GMT 1993

Copyright(C) 1986 - 1993 Thomas Williams, Colin Kelley

Send comments and requests for help to info-gnuplot@dartmouth.edu

Send bugs, suggestions and mods to bug-gnuplot@dartmouth.edu

Terminal type set to 'x11'

gnuplot> plot "<tail +4 adi2.dprof|awk '{print NR,$3+$4,$2}'" with box

For this is a single-threaded application, the information provided by dprof is not of great benefit. But for multi-threaded applications, it can reveal quite a lot. Since access to the local memory is faster than access to remote memories on an Origin system, the best performance on parallel programs which sustain a lot of cache misses will be achieved if you can arrange it so that each thread primarily accesses its local memory. dprof gives you the ability to analyze which regions of virtual memory each thread of a program accesses. Since dprof's utility is primarily for multi-threaded applications, we will postpone a more detailed look at how it can be used until later.

Once the amount of code to be tuned has been narrowed down, it's time to actually do the work of tuning. The most important tool available for accomplishing this is the compiler. Ideally, the compiler should be able to automatically make your program run its fastest. But this simply isn't possible because the compiler does not have enough information to always make optimal decisions.

As an example consider a program which obtains its input data from a file. The size of the data are not known until run time. For those data sets which are too big to fit in cache, the best performance will be achieved if the compiler has performed cache optimizations on the code. But for those data sets which do fit in cache, these optimizations should not be done since they will add overhead and make the program run somewhat slower. So what should the compiler do?

Most compilers are limited in the cache optimizations they can perform, so they optimize for in-cache code; this is the case for the MIPSpro 6.x compilers. The nice aspect of this choice is that it makes it fairly easy to verify that the compiler has properly optimized a program: The transformations it makes apply to relatively small sections of code --- typically loops --- and in the case of the MIPSpro 6.x compilers, "report cards" can be generated to show how well each loop has been optimized. Unfortunately, most data sets don't fit in cache, so the loop-by-loop report cards usually don't indicate the true performance of the program.

The MIPSpro 7.x compilers, however, can perform extensive cache optimizations. If you request the highest optimization level, the compiler will optimize for data which do not fit in cache. This means that the majority of programs will benefit from the cache optimizations. But those programs which operate on in-cache data, or in which the programmer has manually made cache optimzations, may have to pay a performance penalty. Fortunately, this penalty will typically be small compared to the advantage most programs gain from cache optimzations. So, given that the compiler must make a choice, this is on balance the right one. However, it does mean that if you understand what your program is doing, you may be able improve its performance by selectively enabling and disabling the compiler's cache optimizations.

This, of course, applies to the other optimizations as well, and is the subject of the following sections. Coming up, we will look at the types of optimizations the compiler is capable of performing and the switches which enable or disable them. For ease of exposition, we will describe the various optimizations in separate sections as if they are independent of each other. The major categories of optimizations covered will include

In reality, these optimizations are not independent of each other: some loop nest optimizations can enhance software pipelining, and inter-procedural analysis can give the loop nest optimizer more information from which to better do its job. As a result, there is perhaps no best order in which to describe them. The above order is convenient, however, since it starts with operations which are fairly localized (i.e., loops) and then progresses to more complicated and global transformations (i.e., cache optimizations).

This order, however, should not be construed as a ranking of their importance in helping your program achieve its best performance. To the contrary, the loop nest optimzations are probably the most important in this respect since they attempt to make your program more cache-friendly. Since these optimizations can be complicated and understanding them requires a knowledge of how caches work, many users will prefer to just let the compiler accomplish what it can automatically. However, for sophistocated users who wish greater control over cache optimizations, the compiler does allow great flexibility in how they are applied. This topic is significant enough that the loop nest optimizations, along with the principles of cache optimizations, will be discussed in a separate section following the other compiler optimzations.

Given that the various optimizations the compiler will perform can interact with each other, it is impossible to provide a simple formula specifying which optimizations should be attempted in which order to achieve the best results in all cases. Nevertheless, we can make some recommendations which work well in general. A good set of compiler flags to use are the following:

-n32 -mips4 -Ofast=ip27 -OPT:IEEE_arithmetic=3

These flags:

In addition, when linking in math routines, be sure to use the fast math library:

-lfastm -lm

These flags can be used to compile and link in one step:

% cc -n32 -mips4 -Ofast=ip27 -OPT:IEEE_arithmetic=3 \

-o program program.c -lfastm -lm

or separately:

% cc -n32 -mips4 -Ofast=ip27 -OPT:IEEE_arithmetic=3 -c program.c

% cc -n32 -mips4 -Ofast=ip27 -OPT:IEEE_arithmetic=3 \

-o program program.o -lfastm -lm

Using this set of flags will get you a good deal of the way towards optimal performance. For some users, this will be more than adequate, so we will finish this section by first showing you how you can easily get into the habit of using these recommended flags, and after that we will describe them in a little more detail. In the following sections, we'll present material for users who want to know more than just the basic optimization flags.

In order to make using these flags convenient, it is recommended to get

in the habit of defining makefile variables for them. Below is an example

of a good starting point for a Makefile; for a simply-constructed program, this may be all you need:

#! /usr/sbin/smake

#

FC = $(TOOLROOT)/usr/bin/f77

CC = $(TOOLROOT)/usr/bin/cc

LD = $(FC)

F77 = $(FC)

SWP = swplist

RM = /bin/rm -f

MP =

ABI = -n32

ISA = -mips4

PROC = ip27

ARCH = $(MP) $(ABI) $(ISA)

OLEVEL = -Ofast=$(PROC)

FOPTS = -OPT:IEEE_arithmetic=3

COPTS = -OPT:IEEE_arithmetic=3

FFLAGS = $(ARCH) $(OLEVEL) $(FOPTS)

CFLAGS = $(ARCH) $(OLEVEL) $(COPTS)

LIBS = -lfastm

LDFLAGS = $(ARCH) $(OLEVEL)

PROF =

FOBJS = f1.o f2.o f3.o

COBJS = c1.o c2.o c3.o

OBJS = $(FOBJS) $(COBJS)

EXEC = executable

$(EXEC): $(OBJS)

$(LD) -o $@ $(PROF) $(LDFLAGS) $(QV_LOPT) $(OBJS) $(LIBS)

clean:

$(RM) $(EXEC) $(OBJS)

.SUFFIXES:

.SUFFIXES: .o .F .c .f .swp

.F.o:

$(FC) -c $(FFLAGS) $(QV_OPT) $(DEFINES) $<

.f.o:

$(FC) -c $(FFLAGS) $(QV_OPT) $(DEFINES) $<

.c.o:

$(CC) -c $(CFLAGS) $(QV_OPT) $(DEFINES) $<

.F.swp:

$(SWP) -c $(FFLAGS) $(QV_OPT) $(DEFINES) -WK,-cmp=$*.m $<

.f.swp:

$(SWP) -c $(FFLAGS) $(QV_OPT) $(DEFINES) -WK,-cmp=$*.m $<

.c.swp:

$(SWP) -c $(CFLAGS) $(QV_OPT) $(DEFINES) $<

Such a Makefile can even be generated automatically with a simple script, which we call makemake. To use it, create a directory for your program and move the source files

into the directory. Then, if makemake is in your path, you can create a Makefile for the program by simply typing

% makemake executable

where executable is the name you choose for the program. The script will automatically identify

all the C and Fortran files in the directory and list them in the Makefile for you. To build the program, type

% make

and the recommended flags will automatically be used. A version suitable for debugging can be built with the following command:

% make OLEVEL=-g

To add extra compilation options, use the DEFINES variable. For example:

% make DEFINES="-DDEBUG -OPT:alias=restrict"

To remove the executable and objects:

% make clean

The basic optimization flag is -On, where n is 0, 1, 2, 3, or fast. This flag controls which optimizations the compiler will attempt; the higher the optimization level, the more aggressive the optimizations that will be tried. This has an impact on compilation time: in general, the higher the optimization level, the longer the module will take to compile.

Program modules which consume a noticeable fraction of run time should be compiled with the highest level of optimization. This may be specified with either -O3 or -Ofast. Both flags enable software pipelining and loop nest optimizations. The difference between the two is that -Ofast includes additional optimizations such as inter-procedural analysis (-IPA), arithmetic rearrangements which might cause numerical roundoff differences (-OPT:roundoff=3), and interprets ceratin pointer variables as being independent of one another, which allows faster code to be generated (-OPT:alias=typed). In addition, -Ofast takes an optional argument to allow it to specify to which machine it should target the generated code. For an Origin2000, one should use -Ofast=ip27.

For modules which consume a smaller fraction of the program's runtime, the optimization level used is determined by how much time one is willing to allow for compilation. If compilation time is not an issue, it is easiest to use -O3 or -Ofast=ip27 for all modules. If it is desireable to reduce compilation time, a lower optimzation level may be used for non-performance-critical modules. -O2, or equivalently -O, performs extensive optimzations, but they are generally conservative. That is, they almost always improve runtime performance, and they won't cause numerical roundoff differences; sophistocated optimizations, such as software pipelining and loop nest optimzations, are not performed. -O2 takes longer to compile than -O1, so the latter may be used when there is a strong need to reduce compile time. At this level only very simple optimizations are performed.

The lowest optimzation level, -O0, should only be used when debugging your program. The purpose of this flag is to turn off all optimizations so that there is a direct correspondence between the original source code and the machine instructions the compiler generates; this allows a source-level debugger to show you exactly where in your program the currently executing instruction is. If you don't specify an optimization level, this is what you get, so be sure to explicitly specify the optimization level you want.

-r10000, -TARG:proc=r10000 & -TARG:platform=ipxxWhile the R10000, R8000 and R5000 all support the MIPS IV instruction set architecture, their hardware implementations are quite

different. Code scheduled for one chip will not necessarily run optimally

on another. One can instruct the compiler to generate code optimized for

a particular chip via the -r10000, -r8000 and -r5000 flags. When used while linking, these flags will cause libraries optimized

for the specified chip, if available, to be linked in rather than generic

versions; specially optimized versions of libfastm exist for both the R8000 and R10000. An alternative flag, -TARG:proc=(r4000|r5000|r8000|r10000), will generate code optimized for the specified chip without affecting

which libraries are linked in. If -r10000 has been used, -TARG:proc=r10000 is unnecessary.

In addition to specifying the target chip, one can also specify the target processor board. This gives the compiler information about various hardware parameters, such as cache sizes, which can be used in some optimzations. One can specify the target platform with the -TARG:platform=ipxx flag. For Origin2000, -TARG:platform=ip27 should be used.

Note that if the -Ofast=ip27 flag has been used, one does not need to to use the -r10000, -TARG:proc=r10000 or -TARG:platform=ip27 flags.

-OPT:IEEE_arithmeticThis option controls how strictly the compiler should adhere to the IEEE 754 standard. There is flexibility here for a couple of reasons:

do i = 1, nb(i) = a(i)/cenddo

to

tmp = 1.0/c

do i = 1, n

b(i) = a(i)*tmp

enddo

is not allowed by the IEEE standard since multiplying by the reciprocal (even a completely IEEE accurate representation of it) rather than dividing can produce results that differ in the least significant place.